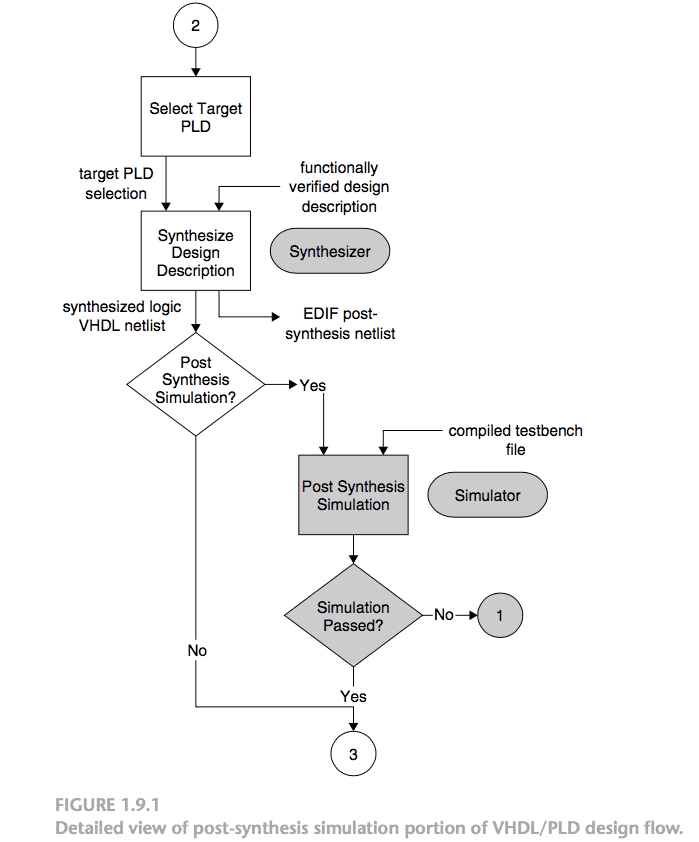

1. A synthesized circuit’s operation may be functionally correct, but it may not meet one or more timing constraints given in its specification. A timing simulation allows us to determine the speed at which the synthesized logic will operate when later programmed into the target PLD.

2, Timing simulations are also referred to as post- route, post-fit, or post-implementation simulations, since the simulation is performed after the synthesized logic has been placed and routed for the target PLD.

3. The VHDL timing model is simulated to provide the timing verification. When we simulate using the VHDL timing model as the UUT, we obtain output waveforms that show not only the functional operation of the design, but also the effects of signal propagation delays through the target PLD.

- An electronic circuit cannot perform its function instantaneously. When the values of inputs to the circuit change, it takes a certain amount of time before a corresponding change occurs at the output. This is called a propagation delay of the circuit.

- The propagation delay consists of two kinds of delays.

- First – each logic element needs some time to generate a valid output signal whenever there are changes in the values of its inputs.

- Second – delay caused by signals as they must propagate through wires that connect various logic elements.

- The combined effect is that real circuits exhibit delays, which has a significant impact on their speed of operation.

- A timing simulator evaluates the expected delays of a designed logic circuit.

- Its results can be used to determine if the generated circuit meets the timing requirements of the specification for the design.

- If the requirements are not met, the designer can ask the physical design tools to try again by indicating specific timing constraints that have to be met. If this does not succeed, then the designer has to try different optimizations in the synthesis step, or else improve the initial design that is presented to the synthesis tools.

Reference: VHDL for Engineers by Kenneth L. Short