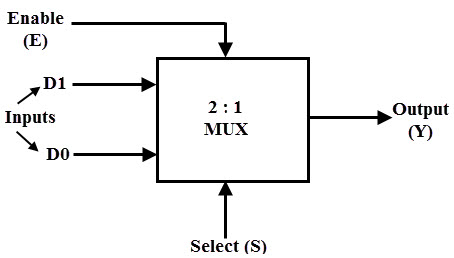

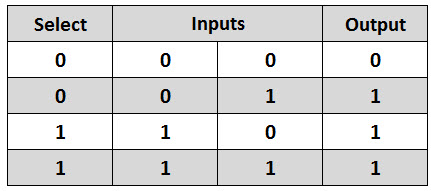

A 2-to-1 multiplexer consists of two inputs, one select input and one output. Depends on the select signal, the output is connected to either of the inputs. Since there are two input signals only two ways are possible to connect the inputs to the outputs, so one select is needed to do these operations.

VHDL Program for 2-to-1 MUX using if-then-else statement:

library ieee;

use ieee.std_logic_1164.all;

entity mux2to1 is

port (w0, w1, s : in std_logic;

f : out std_logic);

end mux2to1;

architecture behaviour of mux2to1 is

begin

process (w0, w1, s)

begin

if s = ‘0’ then

f <= w0;

else

f <= w1;

end if;

end process;

end behaviour;

Just wanted to ask that when we see it’s logic circuit then when s=0 then output should be b w1 rather than w0 ,Is it possible?